【东大新闻网12月30日电】(通讯员 刘斯扬)近日,第68届IEEE国际电子器件年会(International Electron Devices Meeting,IEDM)在美国旧金山举行。东南大学刘斯扬、孙伟锋教授课题组的两项研究成果在此次会议上发表,是东南大学作为第一单位首次在IEDM会议上发表研究成果。

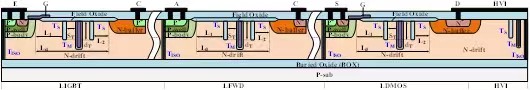

第一项成果题为“41% Reduction In Power Stage Area On Silicon-On-Insulator Bipolar-CMOS-DMOS-IGBT Platform With Newly Developed Multiple Deep-Oxide Trench Technology”,东南大学副研究员张龙、博士生马杰为论文共同第一作者。报道了一种具有多深度氧化沟槽(MDOT)的SOI基Bipolar-CMOS-DMOS-IGBT技术(图1),集成了550V高压LIGBT、LDMOS、FWD及中低压CMOS、BJT等器件,实现了高低压隔离、高压互连线屏蔽以及器件漂移区的大幅缩短。采用MDOT技术能够将单片集成智能功率芯片中的功率级面积缩小约41%。

图1 采用MDOT技术的BCDI工艺平台示意图

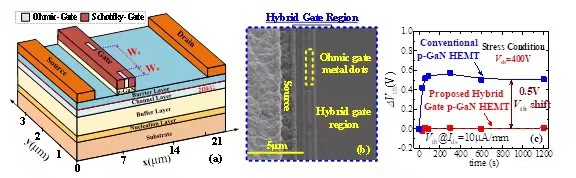

第二项成果题为“Hybrid Gate p-GaN Power HEMTs Technology for Enhanced Vth Stability”,东南大学博士生张弛为论文第一作者。报道了一种提高第三代功率半导体p-GaN HEMT器件阈值电压稳定性的技术——p-GaN栅极混合接触势垒技术(图2),利用势垒较低的局部欧姆接触形成的“电荷泄放”路径,有效抑制了传统p-GaN HEMT中存在的“电荷存储”效应,在维持器件低栅漏电特性的前提下增强了器件阈值稳定性。该技术使得器件在200V、400V反偏应力下阈值电压漂移量分别为0.07V与0.09V;在重复非钳位感性负载应力冲击下,阈值电压漂移量仅为0.03V。

图2 (a)栅极混合接触势垒p-GaN HEMT器件结构(b)混合接触势垒栅结构SEM图(c)400V反偏应力下器件阈值电压漂移量对比

据悉,IEDM始于1955年,是全球报道电子器件最新设计、制造、物理及建模的顶级会议,在学术界及产业界享有崇高的学术地位和影响力。

供稿:电子科学与工程学院

(责任编辑:孙艳 审核:李小男)